A reconfigurable hardware architecture can be adapted post-production, i.e. at start-up-time or even at run-time, to the computational needs. That means, a use-case-optimized circuit is built temporarily by changing the spatial structure (data paths between the computing blocks) and by changing the functionality of the computing blocks themselves. For a new application, the device structure is modified again to operate with optimal computing performance.

Reconfigurable processors are a compromise between computing flexibility and performance. Standardized microprocessors on the contrary are slower and only programmed by sequential instructions but not by modifying all or part of the hardware at compile-time or at run-time. ASICs on the other extreme of the spectrum are produced with highly specialized circuits to perform fixed tasks very efficiently, but unable to be reconfigured for other tasks.

Benefits

- Efficient computing but still versatile functionality: Reconfiguration allows to exploit the given hardware resources optimally at all times, e.g. by parallelizing operations on demand.

- Increased functional density: “The goal is to perform a complex task on a small chip and thus reduce the power consumption, size or weight of the application, even reduce the cost. The application has to be divided into modules whose configurations alternate on the chip. The reconfiguration is performed dynamically at runtime.”

- Increased reliability: When a fault is detected and isolated, a system can be (in some cases) reconfigured to maintain its original function.

- Updating the firmware: “The reconfiguration extends the lifespan of a system. For example,when a new driver or peripheral device is introduced to a system, existing hardware could have a problem to communicate with it. However, if the system is implemented in a reconfigurable chip, the hardware can be updated by simply reprogramming the configuration memory. In this case, the reconfiguration is performed occasionally and only when the application is suspended.”

- Hide circuit functionality: Unveiling a circuit functionality by reverse engineering impossible. Hardware security, Camouflage, IP security

- Adapting hardware: “The goal is to dynamically create electronic circuits that are optimized for a given task, time, and location of the chip.”

- Shortening the design time. “Creating a configuration for a reconfigurable device usually takes much less time than building a new application-specific chip.”

- Cheap production: The standardized layout helps to reduce the production costs by mass manufacturing

Classifications

Granularity

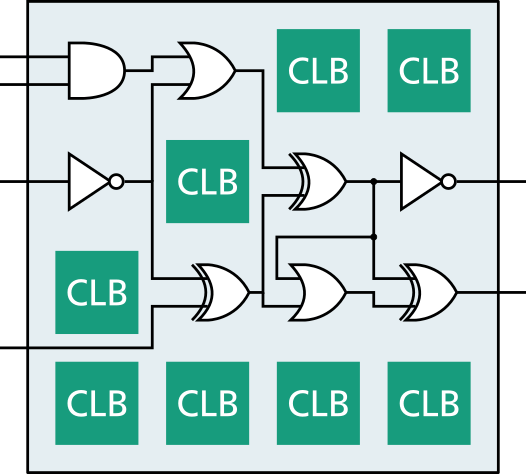

Granularity describes the size of the smallest functional unit that can be addressed by the mapping tool. One can distinguish between coarse-grain (i.e. low granularity), fine-grain and ultrafine-grain reconfiguration. In general, higher granularity provides more flexibility in adapting the circuit to the computational demands. However, also more wiring and switching overhead is needed to interconnect or even reprogram the functional units, which costs additional area, switching time and energy as well as signal transit speed.

Coarse-grain reconfigurable architectures generally have (compared to fine granularity) few, large and multi-purpose logic blocks that operate with word-width (e.g. 32 bit) data and can be connected flexibly.

Fine-grain reconfigurable architectures, have a high flexibility because they can be reconfigured a bit level. The most common example is the field-programmable gate array (FPGA) that uses classical MOSFETs for logic and a look up table for defining the interconnects.

In ultrafine-grain reconfigurable architectures, even the most basic computing elements themselfs can be reprogrammed. One example are polarity-controllable or reconfigurable FETs*.

Other properties

- Reconfiguration frequency

- Static (compile-time reconfiguration): Calculations must be halted to allow for reconfiguration?

- Dynamic (run-time)

- Internal / external reconfiguration: Is the circuit programmed by an external data stream, or does it reconfigure itself?

- Host coupling

- Interconnect architecture

- Island style

- Row-based

- Sea-of-gates

- Hierarchical

- One-dimensional structures

- etc.

Literature

*) also termed electrostatically-doped FET, split-gate FET, SB-MOSFET with field-induced drain, back-enhanced SOI-MOSFET, dual-gate(d) FET or three-independent-gate FET.